#### **General Notes** 1

#### 1.1 **Test Equipment**

#### 1.1.1 Test Equipment for Repairs and Adjustments (see chapters 4 to 7)

The extent to which the SNA-20/-23 can be serviced depends on the test equipment available. The requirements have been split into 4 (+1) stages. The requirements for repair, replacement of printed circuit boards or adjustment of individual subassemblies are listed in chapter 1.2 on page 1-3.

A general check of the instrument should be made after every repair, pcb replacement or adjustment. A generator covering the same frequency range as the SNA is required for this. Refer to chapter 8 for more details.

#### Test equipment required

Requirement 1: (basic equipment) Digital multimeter; 4 1/2 or (preferably) 5 1/2 digits

Oscilloscope (400 MHz, with RF probes)

Frequency counter

Requirement 2:

Requirement 1

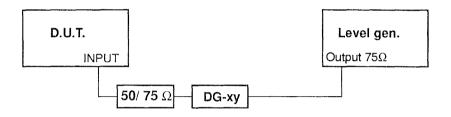

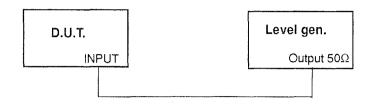

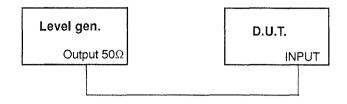

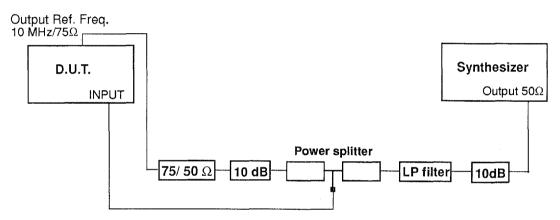

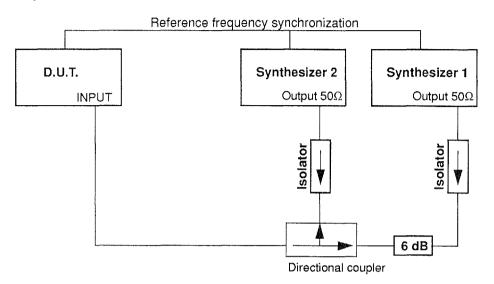

+ Selective level meter, level generator (22 MHz, 50  $\Omega$ ) (e.g. PSM-139 or PS-19/SPM-19 with 2 x ZA 5075)

+ high-impedance probe (TK-11)

+ Spectrum and network analyzer, up to 500 MHz (up to

180 MHz in certain cases only)

e.g. SNA-62 (SNA-1, SNA-2 or SNA-3 in some cases)

Requirement 3:

Requirement 2

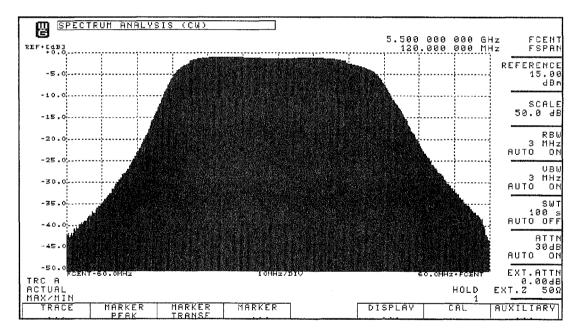

+ Spectrum analyzer (30 GHz [22 GHz])

(e.g. SNA-23/-33, SNA-7)

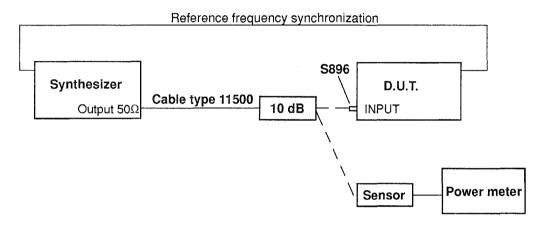

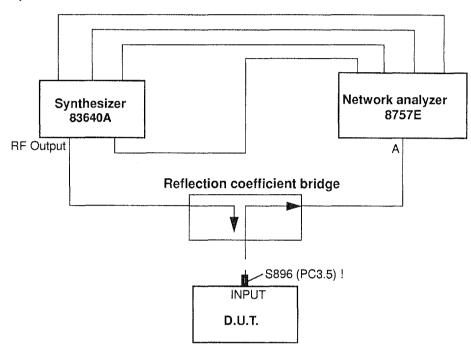

Requirement 4:

Requirement 3

+ Generator (Sweeper)

HP 83640A

+ Power splitter

HP 11667B

+ Power meter

HP 838 A

+ Power sensor

HP 8485 A

+ (10 dB DG HP 8493 C)?

+ Personal Computer PC AT 486 with national IEEE bus

+ Software SWP-XY (for frequency response correction)

Note: Requirement 4 includes the test equipment for measuring

the frequency response.

Other items:

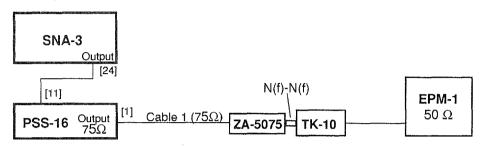

**PSS-16**

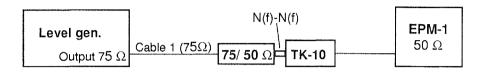

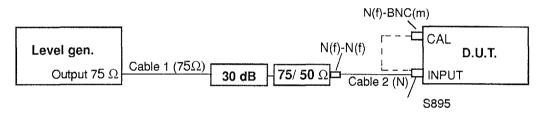

EPM-1

30 dB attenuator (2101-6521.002) Frequency standard (10 MHz ± 10<sup>-9</sup>)

#### Test Equipment for Verifying the Specifications (see chapter 8) 1.1.2

Refer to section 8.2 for details.

## 1.1.3 Accessories / Adapters

| Description                                                                                       | Recommended type /<br>Order no. | Manufacturer |

|---------------------------------------------------------------------------------------------------|---------------------------------|--------------|

| Torque wrench for SMA screw connectors on microwave subassemblies                                 | 0000-7689.262                   | Suhner/W&G   |

| Adapter cable (50-way ribbon cable), link between interface board and measurement unit controller |                                 | W&G          |

| Adapter cable (34-way ribbon cable), link between interface board and measurement unit controller |                                 | W&G          |

| 2 x BNC to MCX plug adapter cables                                                                | 2112-6546.003                   | W&G          |

| BNC to MCX socket adapter cable                                                                   | 2112-6506.014                   | W&G          |

| Adapter board for adjustment of logarithmizer                                                     | Test board 34-2101              | W&G          |

| External AT keyboard (MF-2 compatible)                                                            | Cherry G80 -1000 or similar     | Cherry       |

#### 1.1.4 Service Disk

#### Programs on the service disk

The service disk contains the following programs:

Program name

Use

- EEPROM

For initializing the EEPROM check sums for pcbs where the hardware status is stored in an EEPROM on the pcb itself.

maraware status is stored in an EET Mem on the pob

Form B

For formatting the RAM disk on the memory board.

#### Using the service disk

The service disk is a boot disk, i.e. the operating system (DOS) can be loaded from the disk. If these programs are to be used, please note the following:

- Place the service disk in drive A:\ of the SNA and then switch the SNA on. This ensures that

the operating system is loaded from the disk and the instrument (measurement) software is

not loaded.

- If you want to change from one service program to another, first switch off the instrument and then reboot it from the disk.

- Batch files with the "names" of the service programs are located in the root directory of the disk. These batch files should always be used to start the service programs, as other files in addition to the \*.EXE files are required for running the programs. The batch files load these automatically.

*Important:* The service disk programs may also be used for development purposes in addition to their service functions. Incorrect entries are normally not intercepted by the program, and the plausibility of entries is not checked. These programs do not conform to the general standards of quality which apply to Wandel & Goltermann software products.

## 1.2 Service Scope and Test Equipment Requirements

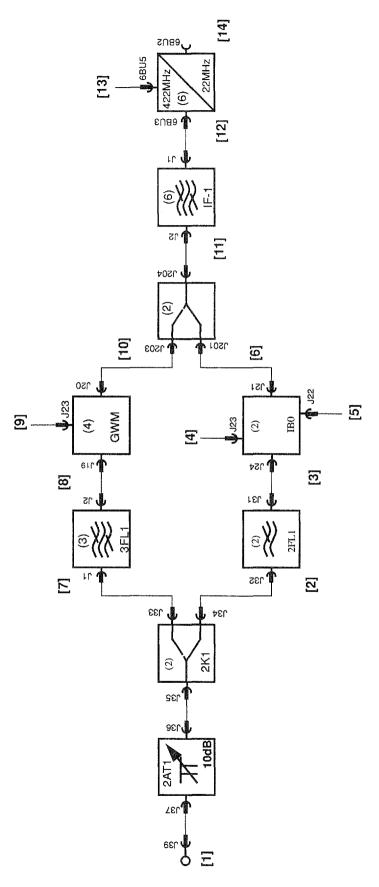

# 1.2.1 Servicing the Input Section Subassemblies

| Circuit<br>board or<br>sub-<br>assembly | Name                                                                                                                                                                         | Service action                 | Test equipment requirement (adjustments required)                             |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------|

| 2 P38                                   | RF converter<br>(Rosenberger)                                                                                                                                                | Subassembly replacement        | Requirement 4 (Frequency response correction)                                 |

| 2 AT1                                   | Attenuator                                                                                                                                                                   | Subassembly replacement        | Requirement 4 (Frequency response correction)                                 |

| 2 FL1                                   | 8 GHz lowpass (Suhner)                                                                                                                                                       | Subassembly replacement        | Requirement 4 (Frequency response correction, input section level correction) |

| 2 K1<br>2101-ZH<br>(2 DX1)              | Coaxial relay<br>(Series A+ B)<br>Diplexer (from series C, re-<br>places coaxial relay 2K1)                                                                                  | Subassembly replacement        | Requirement 4 (Frequency response correction, input section level correction) |

| 2101-ZA                                 | Integration Band 0,<br>complete (Series A to E)                                                                                                                              | Subassembly replacement        | Requirement 4 (Frequency response correction, input section level correction) |

| 2101-ZC                                 | Fundamental mixer, complete                                                                                                                                                  | Subassembly replacement        | Requirement 4 (Frequency response correction, input section level correction) |

| 2101-ZE<br>incl.<br>2101-AQ             | IF switch, complete                                                                                                                                                          | Subassembly replacement        | Requirement 4 (Frequency response correction, input section level correction) |

| 2101-AS1<br>plus<br>3FI1                | Service kit YIG filter control plus YIG filter (YIG filter calibrated and matched with control unit. The YIG correction data are stored in FLASH EPROMS on the control unit) | Subassembly replacement        | Requirement 4 (Frequency response correction)                                 |

| 2101-AR                                 | Input section control                                                                                                                                                        | Repair/Subassembly replacement | Requirement 1 (External mixer bias)                                           |

# 1.2.2 Servicing the Synthesizer Subassemblies

| Circuit<br>board or<br>sub-<br>assembly | Name                                     | Service action                         | Test equipment requirement (adjustments required)                                                       |

|-----------------------------------------|------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------|

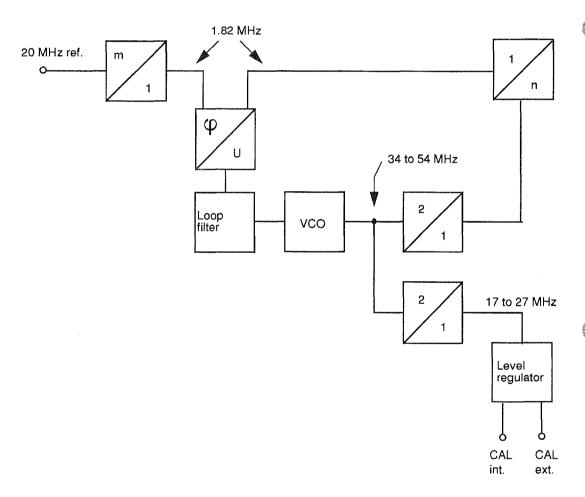

| 2101-B                                  | Time-base / YTO driver                   | Repair/Sub-<br>assembly<br>replacement | Requirement 1 + Spectrum analyzer up to 9 GHz (Requirement 3)  (YTO frequency limits / switching noise) |

| 2101-F                                  | 400 MHz oscillator                       | Repair/<br>Subassembly<br>replacement  | Requirement 1 (LC resonance adjustment)                                                                 |

| 2101-C                                  | Standard frequency adapter (NFO adapter) | Repair/<br>Subassembly<br>replacement  | Requirement 1<br>+ frequency standard<br>(10 MHz std. freq. adjustment)                                 |

| 50 OS1                                  | (YTO) YIG oscillator<br>(Sievers)        | Subassembly replacement                | Requirement 4 (YTO frequency limits, frequency response correction)                                     |

| 2101-A                                  | Synthesizer control                      | Subassembly replacement                | Requirement 1 (no adjustment)                                                                           |

| 2101-ZG                                 | SHF pre-attenuator                       | Subassembly replacement                | Requirement 1 (no adjustment)                                                                           |

| 2101-K                                  | Synchronous attenuator / phase meter     | Subassembly replacement                | Requirement 1 (no adjustment)                                                                           |

# 1.2.3 Servicing the 422 MHz/10 kHz Converter and the IF Measurement Section Subassemblies

| Circuit<br>board or<br>sub-<br>assembly                              | Name                                                                                                                   | Service action                        | Test equipment requirement (adjustments required)                                                                                                                                                       |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

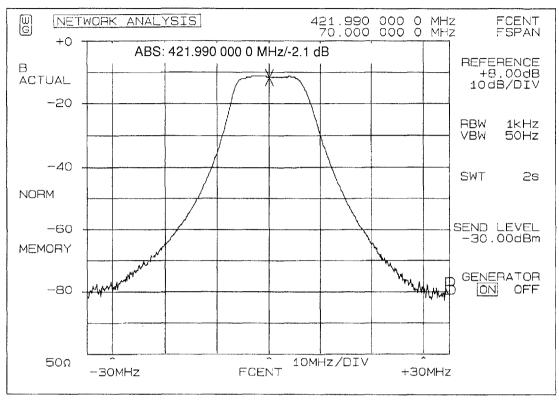

| 6 IF-1                                                               | 422 MHz bandpass (Interdigital filter)                                                                                 | Subassembly replacement               | Requirement 2 (Input section level correction)                                                                                                                                                          |

| 2101-X                                                               | 422/22 MHz converter                                                                                                   | Subassembly replacement               | Requirement 2 (Input section level correction)                                                                                                                                                          |

| 2101-Y                                                               | 422 MHz/10 kHz converter                                                                                               | Subassembly replacement               | Requirement 2 (Input section level correction)                                                                                                                                                          |

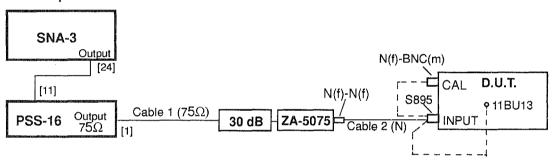

| IF selection,<br>complete<br>2101-L plus<br>5 x 2101-R<br>5 x 2101-S | Service kit IF selection incl. 5 x LC bandpass and 5 x amplifier stage                                                 | Repair/<br>Subassembly<br>replacement | Requirement 2<br>+ PSS-16<br>(IF selection adjustment)                                                                                                                                                  |

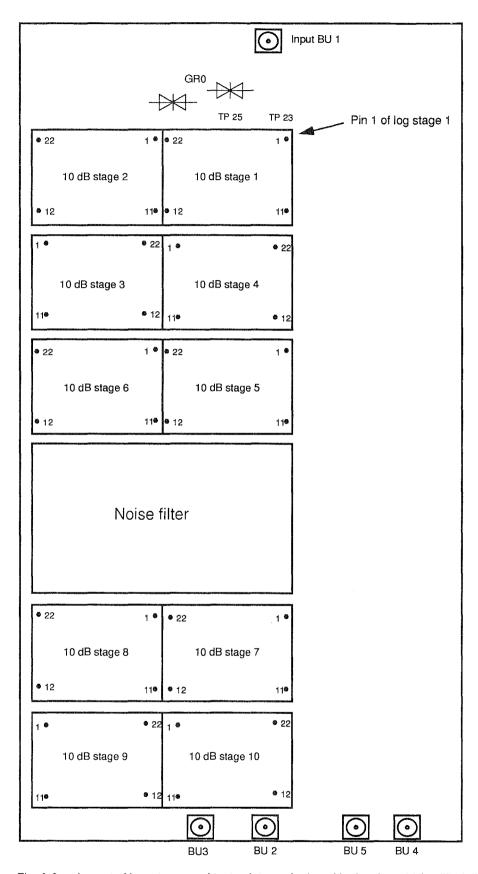

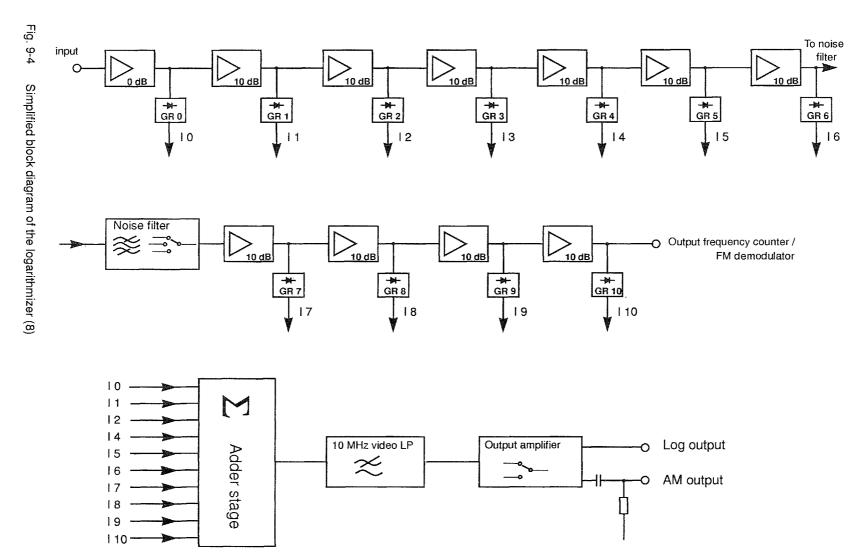

| Logarith-<br>mizer, com-<br>plete<br>2101-M plus<br>10 x 2101-Q      | Service kit Logarithmizer incl. 10 x 10 dB log. stages (The correction data for the logarithmizer are stored on disk.) | Subassembly replacement               | Requirement 2  (Installation of logarithmizer correction data)                                                                                                                                          |

| 2101-O                                                               | Service kit IF converter (Matched subassemblies)                                                                       | Subassembly replacement               | Requirement 1 (no adjustment)                                                                                                                                                                           |

| 2101-P                                                               | Measurement section control                                                                                            | Subassembly replacement               | Requirement 1 (no adjustment)                                                                                                                                                                           |

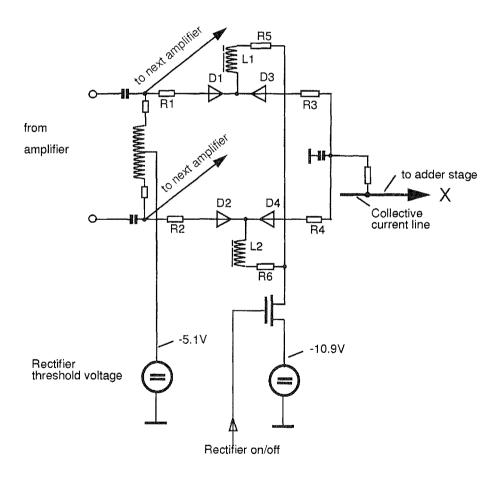

| 2101-N                                                               | Calibration generator                                                                                                  | Repair/<br>Subassembly<br>replacement | Requirement 2 + PSS-16 + EPM-1 + 30 dB DG (2101-6521.002) (or precision power meter, -30 dBm instead of EPM-1, DG and PSS) (Internal and external CAL source level correction) (Demodulator adjustment) |

# 1.2.4 Servicing the Controller Subassemblies

|                                         | Y                               |                                       | γ                                                                                 |

|-----------------------------------------|---------------------------------|---------------------------------------|-----------------------------------------------------------------------------------|

| Circuit<br>board or<br>sub-<br>assembly | Name                            | Service action                        | Test equipment requirement (adjustments required)                                 |

| (18) AT 386                             | AT-CPU (3011-9305.006)          | Subassembly replacement               | Requirement 1<br>(Initialize setup)<br>(Initialize hardware code)                 |

| 4111-A                                  | Screen controller board (BSK-3) | Subassembly replacement               | Requirement 1 (Initialize hardware code)                                          |

| (16) DS 1                               | Electroluminescent display      | Subassembly replacement               | Requirement 1 (no adjustment)                                                     |

| 2101-AO                                 | Connector board                 | Repair/<br>Subassembly<br>replacement | Requirement 1 (no adjustment)                                                     |

| 2101-AG                                 | Interface board                 | Subassembly replacement               | Requirement 1 (Initialize hardware code)                                          |

| 2101-AF                                 | Memory board                    | Subassembly replacement               | Requirement 1 (Load software) (Load compensation data) (Initialize hardware code) |

| 2101-AL                                 | Keyboard controller             | Repair/Subassembly replacement        | Requirement 1<br>(Initialize hardware code)                                       |

| 2101-AJ                                 | Input keyboard                  | Repair/Subassembly replacement        | Requirement 1 (no adjustment)                                                     |

| 2101-AK                                 | Rotary control                  | Repair/Subassembly replacement        | Requirement 1<br>(Offset)                                                         |

| (18) A1                                 | Floppy disk drive               | Subassembly replacement               | (no adjustment)                                                                   |

## 1.2.5 Servicing the Power Supply Unit Subassemblies

| Circuit<br>board or<br>sub-<br>assembly | Name                | Service action                 | Test equipment requirement (adjustments required)   |

|-----------------------------------------|---------------------|--------------------------------|-----------------------------------------------------|

| CG44<br>(Gossen)                        | AC power supply     | Subassembly replacement        | Requirement 1 (Adjust power supply output voltages) |

| 2101-BD                                 | Voltage distributor | Repair/Subassembly replacement | Requirement 1 (Overtemperature cutout)              |

| 2101-BE                                 | 24 / 12 V converter | Repair/Subassembly replacement | Requirement 1 (no adjustment)                       |

## 2 Important Notes

## 2.1 Safety Instructions

## 2.1.1 Preventing Electrical Accidents

#### Safety class

This instrument belongs to safety class I as defined by IEC publication 348 and VDE 0411. The AC line connector shall not be inserted into AC outlets without a protective ground contact, except in specially certified areas.

#### Checks before repairs and maintenance

Checking the instrument construction

No changes in instrument construction which reduce safety may be made.

#### Checking the protective ground

Check the connection and general condition by visual inspection and measure the resistance between the protective ground contact and the AC line plug and the instrument enclosure. The resistance must be  $< 0.1~\Omega$ . Shake the cable during the measurement. Resistance variations mean that the cable is faulty.

#### Checking the insulation resistance

Measure the insulation resistance between the AC line terminals which have been shorted together and the protective conductor terminal of the instrument using a 500 V insulation tester. Ensure that the instrument's AC line switch is in the ON position. The insulation resistance must be  $> 2~\text{M}\Omega$ .

#### Opening the instrument

When covers are removed, or parts are extracted with tools, live components may be exposed. Even contact points may be live.

Therefore, before opening the instrument, disconnect all voltage sources.

If it is absolutely essential to carry out calibration, maintenance or repairs while the instrument is opened and connected to a voltage supply, these procedures may only be carried out by a competent technician who is aware of the associated risks.

Capacitors in the instrument may still be charged; consult the circuit diagrams.

#### **Fuses**

Only specified fuses shall be used.

#### Repairs, replacing components

Repairs must be carried out by a competent technician. No changes in the instrument construction, which reduce its safety shall be made. In particular, this applies to creepage paths and component spacing.

Always use original spare parts whenever possible. Other spare parts may only be used if the safety specifications of the instrument are not reduced.

#### Checks after repairs and maintenance

Check the connection and general condition by visual inspection and measure the resistance between the protective ground contact at the AC line plug and the instrument enclosure. The resistance must be  $< 0.1~\Omega$ . Shake the cable during the measurement. Resistance variations mean that the cable is faulty.

#### Insulation resistance

Measure the insulation resistance between the AC line terminals which have been shorted together and the protective conductor terminal of the instrument using a 500 V DC insulation tester. Ensure that the instrument's AC line switch is in the ON position. The insulation resistance must be > 2  $M\Omega$ .

#### 2.2 Anti-static Measures

Electrostatic charges and fields may damage or destroy semiconductor components.

It is, therefore, essential to protect all semiconductor components in the instrument from electrostatic charges and fields.

When the instrument is in its enclosure, there are no problems. When the instrument is opened, the DIN 40 021 warning symbol on

- boards and

- assemblies

that are sensitive to STATIC reminds you that special protective measures have to be taken.

warning symbol according to DIN 40 021

## Special measures

#### **Grounded person**

Only grounded persons using an anti-static workstation shall work on the instrument.

#### **Grounded bracelet**

A grounded bracelet is used to earth technicians working at anti-static workstations.

#### Conducting work surface

The STATIC workstation comprises a conducting work surface with terminals for the bracelet and ground cable.

#### Ground cable

The ground cable is connected to ground potential. The following reference points provide ground potential:

- the instrument ground connector,

- the protective ground connector,

- other points at ground potential.

#### Soldering station

The soldering station must be connected to ground. The soldering station must be specially designed for semiconductor components that are sensitive to static (zero-voltage circuit, grounded soldering iron bit).

#### Spare parts

Until they are needed, components that are sensitive to static should be left in their protective packaging.

They should only be removed from their protective packaging by a grounded person at an antistatic workstation.

## 2.3 Handling Microwave Subassemblies

Special test equipment and tools are used during production and repair of the microwave subassemblies. For example, the contacts on the ceramic substrate in the microwave subassemblies are made using bonded wires. The semiconductor components used are extremely sensitive to electrostatic charges. For this reason, no components in the microwave circuits should be removed, nor should the power supply (control) board fitted to some modules be removed. Opening these modules will likely result in irreparable damage.

If a fault is present in a microwave module, the module should be replaced completely.

#### Caution!

Opening the microwave modules invalidates the guarantee and repair of the modules in the factory is no longer possible.

#### Handling the microwave step attenuator line

The attenuator (ATTN) is assembled in a clean-room, since even very fine dust particles can adversely affect its performance. Repairs should therefore also be carried out only in a clean-room. Opening the attenuator invalidates the guarantee and repair of the attenuator in the factory is no longer possible.

#### Handling waveguide lines

When removing waveguide lines, the screw connectors at both ends of the line must always be undone to ensure that the SMA plugs and sockets and the waveguide itself are not subjected to mehanical stress. Under no circumstances should the waveguides be bent.

*Important:* The coaxial SMA screw connectors on the microwave modules and waveguides must be tightened to the prescribed torque value. The torque wrench specified in chapter 1.3 should be used for this.

## 2.4 Repair of Circuit Boards Fitted with SMD Components

#### 2.4.1 Introduction

To ensure maximum reliability after repair, particular care and attention are required when working on circuit boards fitted with SMDs<sup>1</sup>. Particular attention should be paid to the method used and the required tools and equipment.

Only persons familiar with SMT<sup>1</sup> should carry out such work. The following rules should be observed:

- a) Use the described test technique for SMDs (see chapter 2.4.2 on page 2-5)

- b) Observe the SMD repair guidelines (see chapter 2.4.3 on page 2-6).

- c) Use only the described SMT soldering and repair methods (see chapter 2.4.4 on page 2-6).

*Important:* If these guidelines are not followed, it is likely that the component or circuit board will be destroyed or damaged. If it is not possible to fulfil the requirements given, it is better to replace the entire board rather than attempt to repair it.

## 2.4.2 Test Techniques for SMD Boards

Never make direct connections (e.g. with a probe) to SMDs when you are checking them out. Instead, use tracks, test pads or vias.

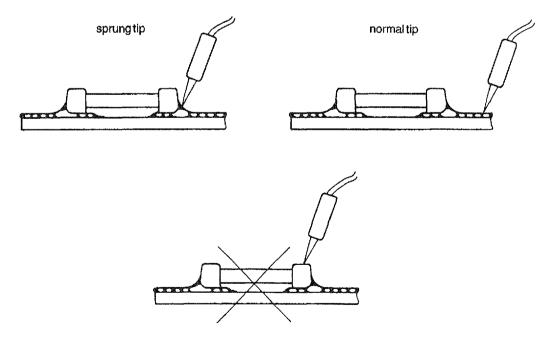

If you are using a special probe with a sprung prod, only make contact at the foot of the component (see figure 2-1).

Fig. 2-1 Making measurements on SMD boards

<sup>1</sup> Note:

SMD = Surface Mounted Device SMT = Surface Mounted Technology

## 2.4.3 Repair Guidelines for Boards with SMDs

If SMDs are handled incorrectly, their properties may be adversely affected. Particular care should therefore be taken. For example, even minimal dirt or impurities on the SMD contacts (e.g. a fingerprint) will prevent wetting during soldering and result in dry joints. The spaces between contacts are often so small that short-circuits are easily caused by solder tracks between them due to the use of unsuitable tools.

The following rules should therefore be observed:

- Only use tools and equipment specially designed for SMD.

- Preferably use special SMD tweezers.

- Do not modify the SMD in any way (use as supplied).

- Keep the SMD in its original packaging until required (the values are not marked on the components!).

- Never hold SMDs with your bare hands.

- Never touch the contacts of SMD with anything other than the special tools (tweezers, clips) intended for this purpose.

- If an SMD is dropped, it should be thrown away (hair-line cracks are likely, particularly in larger components).

- Use only special test tweezers, etc., for checking the value (R or C, etc.) or identity of SMDs which are not mounted on a board.

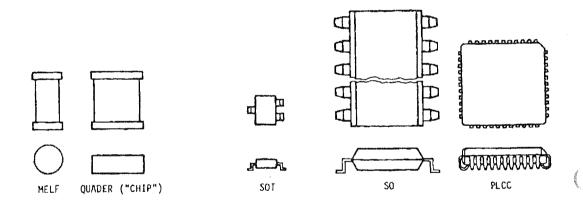

Fig. 2-2 Various SMD outlines

## 2.4.4 SMT Soldering and Repair Procedures

The object of these procedures is to eliminate soldering faults or to replace defective SMDs. Board faults are eliminated using conventional methods.

When you repair an SMD board, there is a considerably greater risk that components or the board will be damaged. The second eventuality is particularly important because if, say, soldering pads are torn off, it is impossible to mount any SMD without using special adhesive techniques. The board would, therefore, have to be thrown away (see under "Repairing torn-off soldering pads").

#### Observe the following special SMT rules when carrying out work of this kind

- Soldering iron temperature (bit) = 290 °C (max. 300 °C)

- Maximum temperature of hot gas equipment is 400 °C

- Maximum soldering time 3 s (time for which the solder liquefies)

- Only attempt to repair an SMD once; i.e. do not resolder SMDs which have been unsoldered by mistake, always replace them

- Flux may be used

- Solder paste may be used

- Wire solder may be used

#### **Unsoldering SMDs**

- SMDs without pins (Melf + chip) (see Figure 2-2)

Unsoldering is carried out with hot gas or soldering tweezers. When the component has been removed, the pads must be sucked clear with a desoldering station (fine bit) or a hand desolderer.

- SMDs with a small number of pins (less than 6 pins, SOT, etc.).

- Hot gas is used or the pins can be cut through as with multi-pin ICs.

- SMDs with many pins (more than 6 pins, SO, PLCC) Hot gas is used. A simple hot gas station with small hot air jets is not sufficient. It is only possible to remove ICs of this kind, without damaging the board, by using expensive equipment which heats up all the pins at the same time. If you do not have soldering equipment of this type, cut through the pins directly at the component using a cutter, unsolder the pins in the board and suck the solder from the pads.

#### Soldering SMDs into position

- SMDs without pins

Use hot gas. The solder must be flowing on both pads simultaneously.

- SMDs with pins

Use a miniature soldering iron or hot gas. Diagonally opposite IC pins must be soldered alternately.

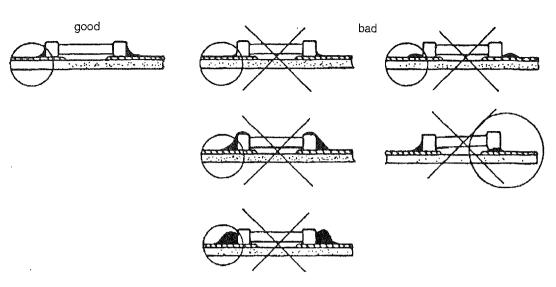

- Check the joint with a magnifying glass (see Figure 2-3) for bridging, dry joints, cracks and holes, the soldering surface (smooth and evenly shiny), solder drops, splashes and the correct positioning of the SMD.

Fig. 2-3 Examples showing soldered SMDs

#### Repairing torn-off soldering pads

If a soldering pad for an SMD component with pins (IC, PLCC, SOT etc.) has been torn off, solder the component to the board following the usual guidelines and repair the defective pad in the following way:

A varnished wire (d = 0.2 mm) is connected from the component pin to a place of contact near the pad. It is best to use a via. If this is not possible, the wire can be soldered to a soldering pad (as large as possible) of an SMD component.

In the case of SMDs without pins (mini melf / melf resistors, diodes tantalum/multi-layer capacitors, chip resistors, C trimmers, etc.), measures must be taken to ensure the mechanical stability of the soldered joint if a soldering pad is missing.

- 1 Solder one side of the component to a soldering pad. Connect the other side to a via or an SMD soldering pad which should be as large as possible with a wire (d = 0.6 mm, if necessary insulated). The wire should not be longer than 10 mm.

- 2 If the method of repair described in 1. cannot be used, the component is held in place with an adhesive.

- Dot the adhesive on the board.

- Place component on board.

- Cure adhesive (100 °C, 20 min).

- Solder wire (varnished, 0.2 mm) to SMD pin and connect to suitable contact point.

If there is no suitable contact point near the repair, or it is essential to use connections of minimum length, any wide tracks can be used or the solder resist and the black oxide can be scratched from any convenient area and the wire soldered to it.

Recommended solder: wire solder, SnPb 63 d = 0.6 mm or d = 0.3 mm with FSW-32 flux.

## 2.5 Cleaning the Front Panel and Casing

Never use organic solvents or proprietary cleaning fluids for cleaning the front panel and casing.

The best cleaning fluid is warm water to which a drop of detergent has been added. Use this to slightly dampen a clean cloth. Make sure that no water enters the instrument. To ensure that drying marks are not present, wipe the instrument with a dry cloth after cleaning it.

## 3 Mechanical Construction

#### 3.1 Instrument Codes

The following instrument codes should be stated when you make enquiries about the instrument or order spare parts:

Type designation, serial number, special version designation, software version number and fitted options.

e.g.: RFS-1, series C-123, BN 2112/03, software (master) V 04.01

When ordering spare parts, the item number given in the parts list in the Annex must also be stated.

e.g.: 1 transistor BCY 59 D, item no.:0001-0016.518

The serial number will be found on the front panel below "RFS-1".

The version number is on the back panel.

## 3.1.1 Determining the Hardware and Software Status

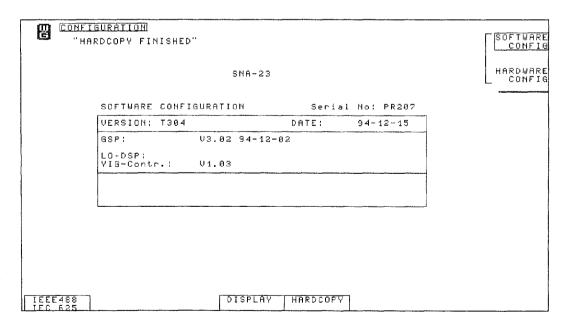

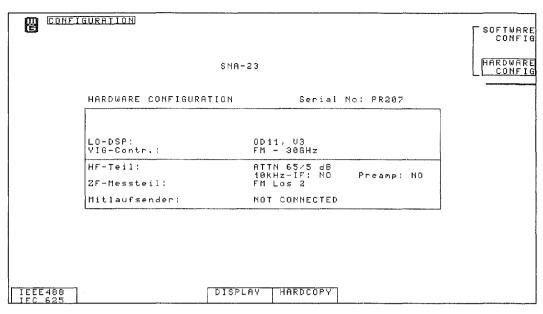

The hardware and software status of the SNA can be displayed on the screen using the MODE/CONFIGURATION menu. The hardware and software status must be quoted in all queries regarding the instrument. The menus for displaying the hardware and software status are shown in figure 3-1 and figure 3-2.

Fig. 3-1 Menu for displaying SNA software status (Example: SNA-23)

Fig. 3-2 Menu for displaying SNA hardware status (Example: SNA-23)

Some hardware errors may make it impossible to display the software and hardware status of the instrument using the menu, e.g. when the instrument software crashes directly after starting (2101 Debug Output appears in the display). In such cases, the software status can be determined by displaying the files B:\123Time and C:\123Time. C:\123Time contains the information for the instrument software status (AT-CPU and BSK-3 graphics software). B:\123Time contains the information regarding the "layout" of the correction data tables contained on the COMPEN-SATION DATA DISK and which are copied in the SRAM of the memory board (17). When the DOS prompt is displayed on the screen, the file contents can be displayed by selecting the drive (B:\ or C:\) and then entering <Type 123Time> (using an external keyboard). This will only work if the AT-CPU is working correctly and drives B:\ and C:\ (board (17), Memory) can

```

GSPV: 3.02 [Graphics software version]

GSPD: 94-12-02 [Graphics software date]

ATV: T304 [Instrument software version (AT-CPU)]

ATD: 94-12-15 [Instrument software date (AT-CPU)]

```

be accessed properly. Example displays of these files are shown in figure 3-3 and figure 3-4.

Fig. 3-3 Display of C:\123Time (example)

```

94-05-11

released: 94-05-11 (2.5)

released: 94-04-22 (2.4)

released: 94-03-28 (2.2)

```

Fig. 3-4 Display of B:\123Time (example)

## 3.2 Assembly/Disassembly Instructions

## 3.2.1 Disassembling the Instrument Chassis

#### Removing the casing cover

To remove the casing cover, unscrew the six hex-key (allen) screws (M4, SW3). Then push back and remove the two impact protector corner pieces. The casing cover can now be removed carefully.

#### Removing the chassis from the casing

Remove the casing cover as described above and place the instrument top side down on the workbench. Carefully lift the casing off the chassis.

#### Caution!

Make sure that the input sockets and rotary control of the instrument are not subjected to strain. Never hold or lift the instrument using these parts, as damage is likely to result.

## 3.2.2 Opening the Fold-Out Chassis

The instrument chassis folds out for servicing and maintenance. This provides access to all circuit parts.

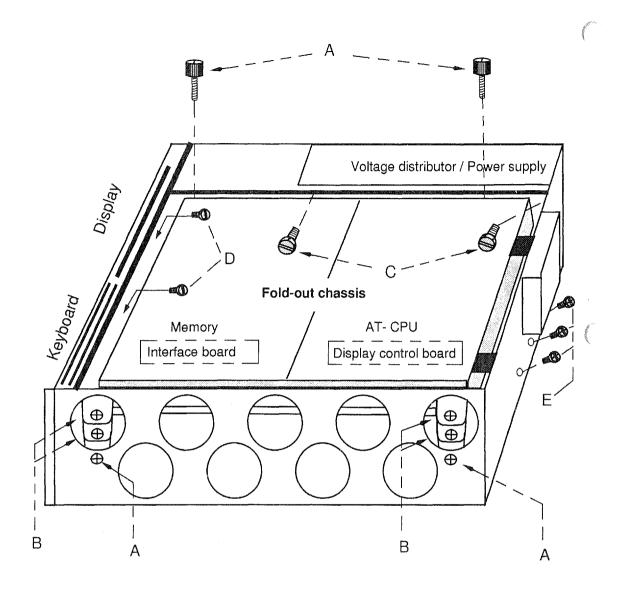

Before opening the chassis, remove the instrument from the casing (see chapter 3.2.1). To open the fold-out chassis, loosen the two knurled screws (between the power supply/voltage distribution board and the fold-out chassis) and undo the two crosshead screws (M3; on the right-hand side of the instrument). These screws are indicated by "A" in the diagram (see figure 3-5 on page 3-4). The chassis can now be folded out completely. The strut on the right-hand side of the instrument can be used to lock the fold-out chassis in the open position for servicing.

The fold-out chassis can be divided into three separate chassis plates by removing a further eight crosshead screws (4 screws on each side of the chassis). Only the screws on the right-hand side of the instrument are shown in figure 3-5 (marked "B").

#### Caution!

When reassembling the fold-out chassis, make sure that the original screws or screws of exactly the same length are used. *Longer screws will likely result in a short circuit!*

#### Service position

The instrument can be operated with the chassis folded out when placed normally on the work-bench. It can also be operated when placed on its right-hand side with the chassis folded out. It should not be operated for any length of time when placed on its left-hand side (power supply side), as the flow of air to the power supply is hindered: the power supply may overheat and the instrument may switch off automatically.

Fig. 3-5 Diagram of instrument showing screws securing the fold-out chassis and the power supply and synthesizer modules (fold-out chassis screening cover removed).

## 3.2.3 Positions of the Subassemblies

#### List of boards

| Name                          | Code     | For location, refer to |

|-------------------------------|----------|------------------------|

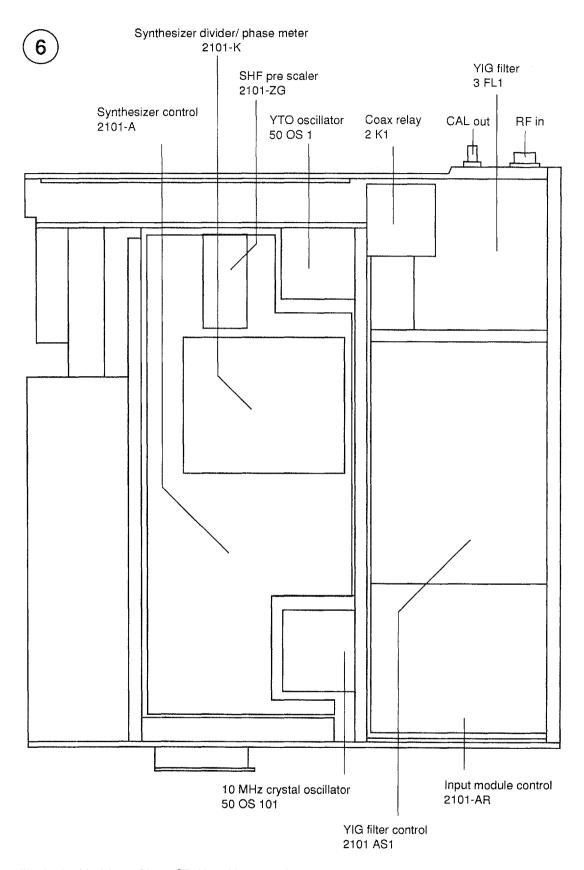

| Synthesizer control           | 2101-A   | page 13                |

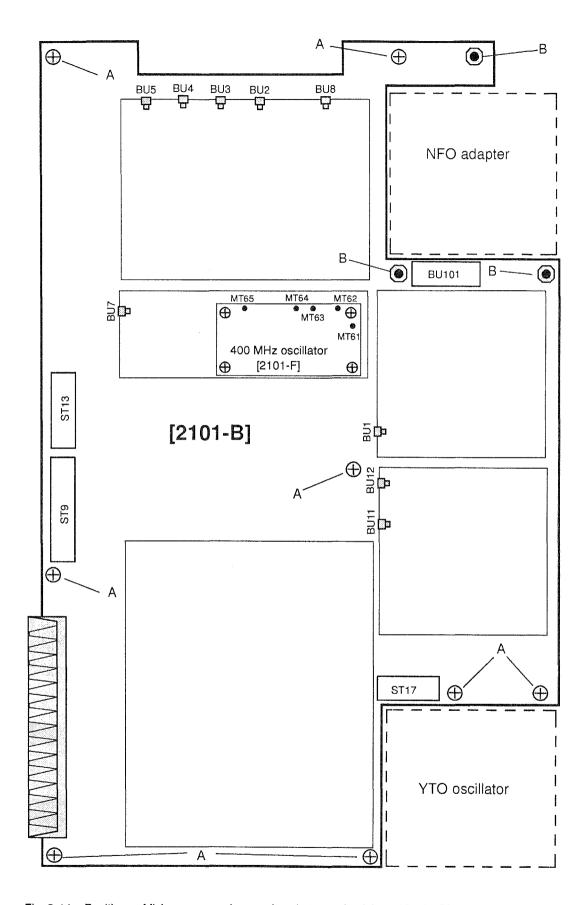

| Time base/YTO driver          | 2101-B   | page 11                |

| 400 MHz VCO                   | 2101-F   | page 11                |

| Sync. divider/phase meter     | 2101-K   | page 13                |

| IF selection                  | 2101-L   | page 9                 |

| Logarithmizer                 | 2101-M   | page 9                 |

| Calibration generator         | 2101-N   | page 8                 |

| IF converter                  | 2101-O   | page 8                 |

| Measurement module control    | 2101-P   | page 8                 |

| 10 dB log stage               | 2101-Q   | page 9                 |

| LC bandpass                   | 2101-R   | page 9                 |

| Preamplifier stages           | 2101-S   | page 9                 |

| 422/22 MHz converter          | 2101-X   | page 10                |

| 422 MHz/10 kHz converter      | 2101-Y   | page 10                |

| 422 MHz bandpass              | IF-1     | page 10                |

| Memory board                  | 2101-AF  | page 7                 |

| Interface board               | 2101-AG  | page 7                 |

| Input keypad                  | 2101-AJ  | page 7                 |

| Rotary control                | 2101-AK  | page 11                |

| Keyboard controller           | 2101-AL  | page 11                |

| Connector board               | 2101-AO  | page 8                 |

| Input module control          | 2101-AR  | page 13                |

| YIG filter control            | 2101-AS1 | page 13                |

| 12/24 V converter             | 2101-BE  | page 8                 |

| Voltage distribution          | 2101-BD  | page 7                 |

| Power supply                  | CG-44    | page 7                 |

| NFO adapter                   | 2101-C   | page 11                |

| Display control board (BSK-3) | 4111-A   | page 7                 |

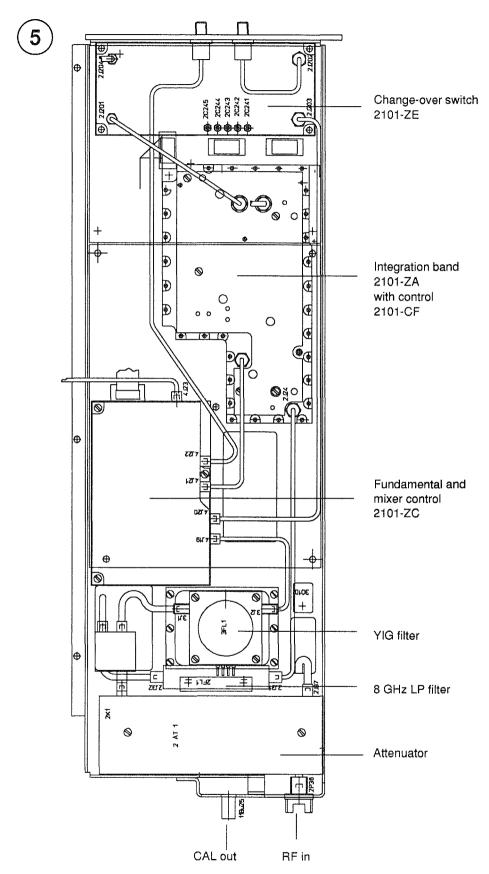

| Integration band 0            | 2101-ZA  | page 12                |

| Integration band 0 control    | 2101-CF  | page 12                |

| Fundamental mixer             | 2101-ZC  | page 12                |

| Fundamental mixer control     | 2101-AV1 | page 12                |

| IF change-over switch         | 2101-ZE  | page 12                |

| 10 MHz crystal oscillator     | 50 OS101 | page 13                |

| Coaxial relay                 | 2K1      | page 13                |

| YIG filter                    | 3 FL1    | page 13                |

| SHF pre-scaler                | 2101-ZG  | page 13                |

The current designations (index) are found in the parts list in the Annex to the Service Manual. (Section "Parts Lists")

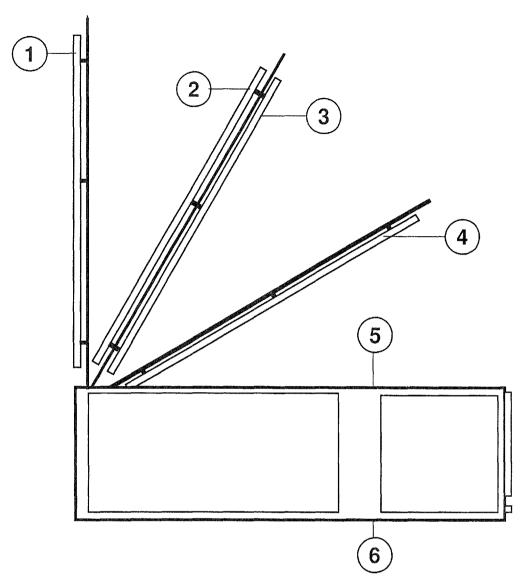

Fig. 3-6 Side view with chassis open

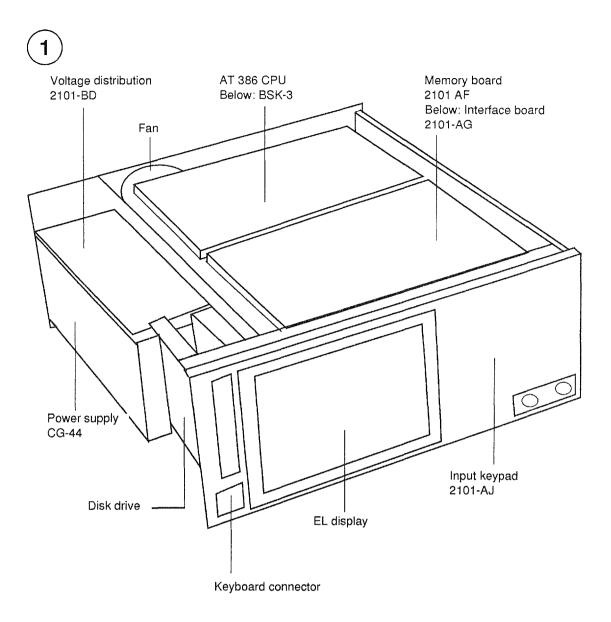

Fig. 3-7 Module positions: AT 386 CPU, Memory board, BSL Interface board, PSU distribution, PSU and Input keypad

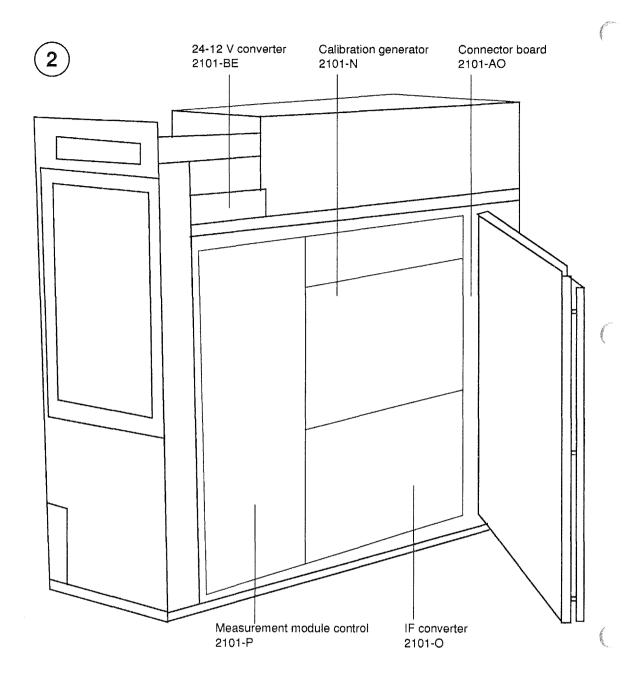

Fig. 3-8 Module positions: Calibration generator, IF converter, Measurement module control and 24-12 V converter

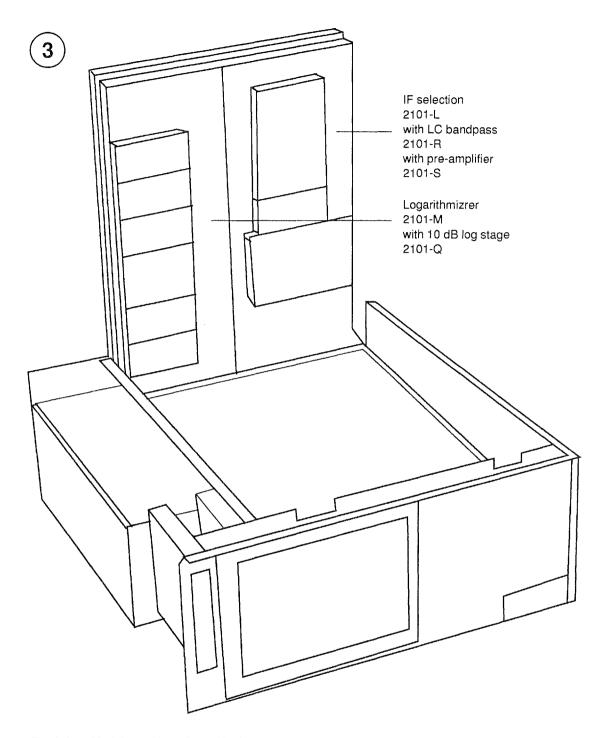

Fig. 3-9 Module positions: Logarithmizer and IF selection

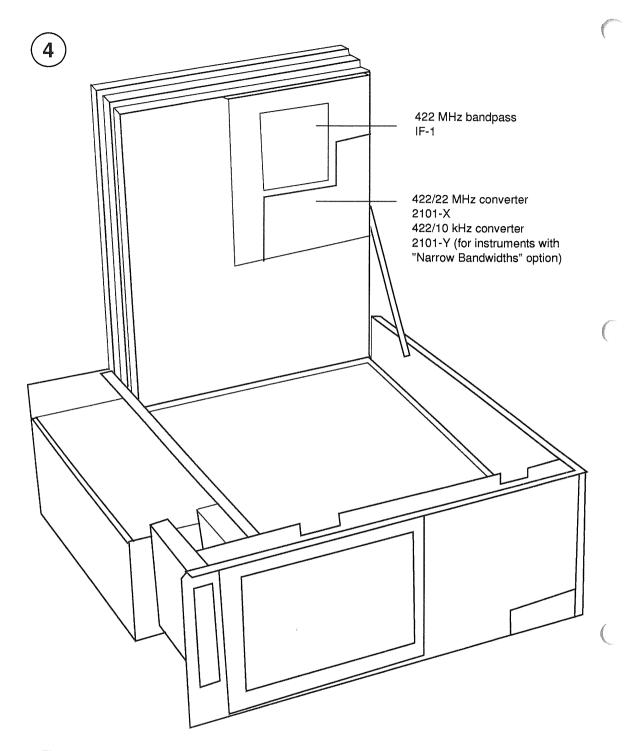

Fig. 3-10 Module positions: 422 MHz bandpass and 422/22 MHz converter

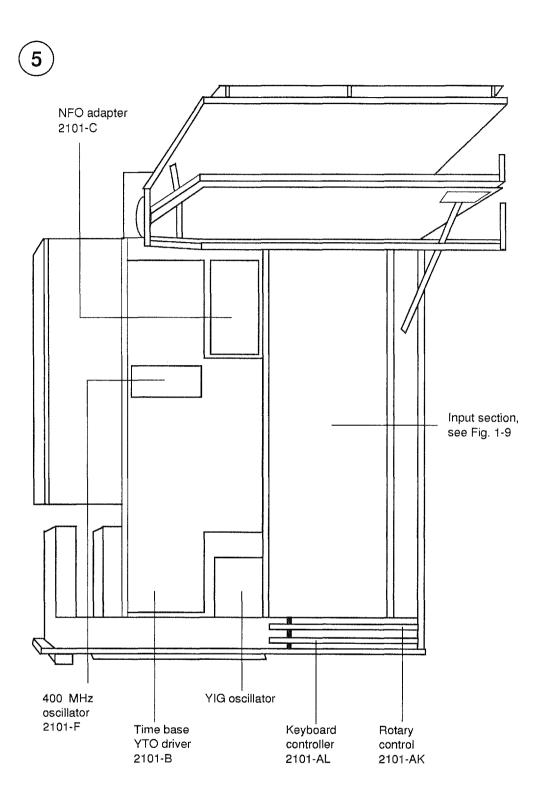

Fig. 3-11 Module positions: OD-11 and input section seen from above

Fig. 3-12 Input section, seen from above

Fig. 3-13 Module positions: OD-11 and input section seen from below

## 3.2.4 Removing Circuit Boards and Subassemblies

The safety regulations and protective measures described in chapter 2 should be observed when removing circuit boards and subassemblies. In particular, the regulations for "Preventing Electrical Accidents" and the "Anti-static Measures" must be observed.

#### Caution!

The memory board contains a battery-buffered RAM in which instrument-specific correction data for the frequency response and logarithmizer are stored along with user setups. A back-up copy of this data must be made before any circuit boards in the region of the memory board are removed, to allow the data to be restored if the RAM power supply is interrupted.

## 3.2.4.1 Removing Microwave Subassemblies and Modules

When removing microwave subassemblies and modules the following additional measures must be observed:

- "Anti-static Measures" on page 2-3

- "Handling Microwave Subassemblies" on page 2-4

- "Handling the microwave step attenuator line" on page 2-4

- "Handling waveguide lines" on page 2-4

## 3.2.4.2 Removing the AT-CPU and Memory Boards

Please observe the information in chapter 3.2.4 and chapter 3.2.7.

First remove the aluminium screening cover of the fold-out chassis. To do this, place the chassis in the service position and lock it in position. Then undo a total of 14 cross-head screws. The screen cover can then be lifted off. After this, unplug all the electrical connectors (ribbon cables) connected to the board which is to be removed.

The AT-CPU and Memory boards are connected together electrically only via the two 3-row edge connectors (48-way and 96-way). If one of these boards is to be removed, the screws (spacing bolts) on the other board should also be undone to prevent mechanical stress during the dismantling procedure.

When refitting either of these boards, first mate the dge connectors together carefully and then tighten-up the spacing bolts. This avoids stressing the boards mechanically.

## 3.2.4.3 Removing the Interface Board and Display Control Board

Please observe the information in chapter 3.2.4 and chapter 3.2.7.

Before either of these boards can be removed, the AT-CPU and Memory boards must be removed (see chapter 3.2.4.2). The interface board and display control board are also linked via two 3-row edge connectors (48-way and 96-way). Use the same procedure for removing these boards as that described in chapter 3.2.4.2.

## 3.2.4.4 Removing the Power Supply Unit and Voltage Distribution Board

- Remove the instrument chassis from the casing (see chapter 3.2.1)

- Fold out the chassis and lock it in the service position (see chapter 3.2.2)

- Undo the two screws (M4) holding the power supply to the aluminium separator plate (screws C in figure 3-5 on page 3-4)

- Unplug the following connectors from the voltage distribution board: ST7, ST8, ST9 St10, BU2, BU3, BU4, BU5, BU6, Bu11 and BU12

- Carefully slide the power supply unit approx. 1 cm towards the front of the instrument, until

the steel casing of the power supply is clear of the four tabs on the aluminium separator

plate.

- Carefully pull out the power supply unit towards the left-hand side.

To remove the voltage distribution board, first unplug the two connectors ST/BUX1 and ST/BUX2 from the power supply unit and undo the 5 cross-head screws. The circuit board can now be detached from the power supply unit.

## 3.2.4.5 Removing the Synthesizer

The instrument chassis must first be removed from the casing in order to remove the complete synthesizer or synthesizer subassemblies (see chapter 3.2.1). The subsequent procedures are detailed under the various sub-headings which follow.

#### Removing the complete synthesizer

To remove the complete synthesizer, including the SHF preattenuator, YTO adapter and NFO adapter, proceed as follows:

- Unscrew and remove the lower part of the printed back panel cover

- Fold out the chassis and lock it in the service position (see chapter 3.2.2 on page 3-3)

- Remove the two cross-head screws on the aluminium separator plate between the Display/ Keyboard and Fold-out chassis/Synthesizer (screws D in figure 3-5 on page 3-4)

- Place the instrument on its left-hand side (power supply side)

- Unscrew the waveguide cable between the SHF pre-attenuator (J2) and the fundamental mixer and remove it carefully without bending it.

- Remove the three countersunk screws holding the aluminium fixing brackets between the back panel and the synthesizer (screws located under the previously removed panel cover, screws E in figure 3-5 on page 3-4)

- Unplug the following connectors on the synthesizer control board (51) [2101-A]:

ST1, ST2, ST3 and ST7

- Unplug ST13 (50ST13) from the time base /YTO driver board [2101-B] (see figure 3-14)

- Unplug the MCX plugs from the following sockets on the time base/YTO driver board [2101-B]:

BU1, BU3, BU4, BU5, BU7, BU8, BU11 and BU12

The complete synthesizer can now be removed carefully in the direction of the instrument base (first press the synthesizer on the instrument back panel down towards the instrument base).

*Important:* The waveguide between the SHF pre-attenuator (J2) and the fundamental mixer must be unscrewed or reconnected using a torque wrench (e.g. Suhner wrench, order no. 0000-7689.262).

#### Removing the NFO adapter board [2101-C]

The 10 MHz standard frequency oscillator is mounted (soldered) on the NFO adapter board. The NFO adapter is mounted on the board [2101-B] with three cross-head screws and spacer bolts. Undo the screws (B in figure 3-14) and pull the NFO adapter up to disconnect ST/BU 101.

#### Removing the time base/YTO driver board [2101-B]

The time base/YTO driver board [2101-B] is mechanically linked to the control board [2101-A]. All of the screws and electrical connectors which must be undone in order to remove the board are shown in figure 3-14 on page 3-17.

- Fold out the chassis and lock it in the service position (see chapter 3.2.2 on page 3-3)

- Remove the NFO adapter.

- Unscrew the three spacing bolts to which the NFO adapter was fitted

- Unplug the connector to the YTO oscillator (ST17)

- Remove the eight cross-head screws (M3, screws A in figure 3-14)

- Unplug ST13 and ST9 from [2101-B]

- Unplug the MCX plugs from the sockets on the time base/YTO driver board [2101-B] (see figure 3-14):

- BU1, BU3, BU4, BU5, BU7, BU8, BU11 and BU12

The circuit board can now be pulled upwards carefully to remove it.

#### Caution!

The time base/YTO driver board [2101-B] is stuck to the control board [2101-A] with a strip of conducting aluminium adhesive tape (attached to the screening covers). Lift the tape off carefully on one side when dismantling the assembly. When reassembling [2101-B], make sure that the adhesive tape is stuck back on to the screening covers again.

#### Removing the synthesizer divider/phase meter board [2101-K]

The synthesizer divider/phase meter board [2101-K] is attached to the control board [2101-K] by eight cross-head screws M3. The electrical connections can only be disconnected when the time base/YTO driver board [2101-B] has first been removed. To remove board [2101-K] proceed as follows:

- Remove the time base/YTO driver board [2101-B].

- Remove the eight cross-head screws on board [2101-K]

- Disconnect the electrical connections to board [2101-K] (MCX plug, ribbon cable and five soldered connections)

#### Removing the YIG oscillator (YTO)

The oscillator is contained in an aluminium casing for screening purposes. To remove the YTO, this casing must first be removed. To do this, first remove the complete synthesizer, after which the screen and the YTO can be removed.

#### Removing the 400 MHz oscillator board [2101-F]

The 400 MHz oscillator board [2101-F] is mechanically linked to the time base/YTO driver board [2101-B] by four cross-head screws. The position of the board is shown in figure 3-14 on page 3-17. To remove the board, first remove the screening cover from the frame and undo the four cross-head screws on board [2101-F]. The electrical connection to [2101-B] is by means of 5 solder pins (MT61 through MT65 in figure 3-14). Carefully unsolder these pins before removing board [2101-F].

Fig. 3-14 Positions of fixing screws, plugs and sockets on circuit board [2101-B]

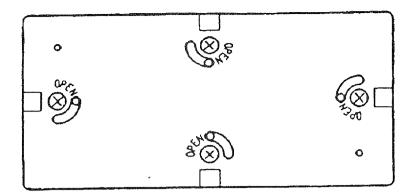

## 3.2.5 Fitting/Removing the Screening Can Covers and Hoods

Fig. 3-15 Screening can cover

#### Opening the cover of the modular screening can

The screening cans are opened with a cross-head screwdriver. The latches are opened by giving the screw about a half turn (pin in the OPEN position).

#### Caution!

If you turn the screw too far, the locking disks may fall off and cause a short circuit.

#### Closing the covers of modular screening cans

Before replacing the cover on the can, set all latches to OPEN (pin). This ensures that the cover fits tightly on the can giving effective screening. Then close all latches and screw down with a torque of 100 Ncm  $\pm$  5 Ncm (torque screwdriver).

#### Removing the hoods of the modular screening system

The screws in the hoods are removed with a cross-head screwdriver.

#### Fitting the hoods of the modular screening system

The screws in the hoods are tightened using a torque of 70 Ncm  $\pm$  5 Ncm (torque screwdriver).

*Important:* If covers and hoods are not fitted correctly, the instrument may malfunction severely.

## 3.2.6 Replacing the A.C. Line Fuse

Refer to section 8 of the operating manual under the heading "Changing the fuse".

### 3.2.7 Replacing the Memory Buffer Battery

A lithium battery is plugged on to the memory board (17). This battery provides power for buffering the RAM when the instrument is switched off. The RAM contains the instrument-specific correction data and the user setups, among other things. If the lithium battery is removed when the instrument is switched off, this data will be lost within a few seconds.

If the battery is to be replaced as a precaution during repairs (average battery life is about 5 years) the user setups should first be saved on a floppy disk (see chapter 4.8).

### Caution!

Before replacing the battery, make sure that the "Compensation Data Disk" belonging to the instrument is available and free of errors, so that the correction data tables can be re-loaded into the RAM after the battery has been replaced (see chapter 4.7). If the "Compensation Data Disk" is not available, a back-up copy of the RAM disk (battery-buffered RAM) must be made so that this can be copied back into the RAM disk after replacing the battery (see chapter 4.9).

## 4 Power-On Test, Error Messages, Software Configuration

### 4.1 Normal SNA Boot-Up Behavior (Series A to E)

The power-on (boot-up) behavior of the SNA-20/-23 is described below. The following conditions must be fulfilled for the instrument to behave as described:

- Instrument must be from series A through E (fitted with CPU "STANDARD SYSTEM MODULE 386 WGR" (3011.9305.006)).

- Instrument is OK (no faults detected during switch-on (BIOS) test).

- There is no (bootable) disk in the SNA-20/-23 floppy drive.

- No key is pressed on the built-in or external keyboard during the boot-up procedure.

The following messages are displayed on the screen after switching on if these conditions are met. Short descriptions of the actions currently being performed by the SNA are shown to the right of the screen messages.

*Note:* The messages displayed may differ slightly from those depicted here, as they depend on the display board and AT-CPU BIOS versions used.

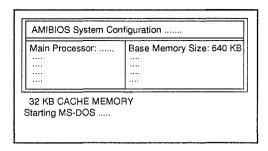

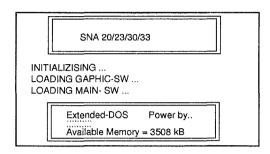

After power-on, the AT-CPU loads the VGA BIOS (BSK-3) and the extended BIOS for the memory board (17). If the memory board extended BIOS loads successfully, the AT-CPU can access drives C: (Flash ROM disk) and B: (battery-buffered SRAM segment on the memory board). This automatically starts the BIOS test (POWER-ON TEST).

The crossover switch on the display control board (BSK-3) is set to VGA ---> EL. This means that all output to the built-in EL display is generated by the VGA module on the display control board (BSK-3). Output to any externally connected monitor is via the graphics processor (TI processor) of the BSK-3.

AMIBIOS (C) 1992 American Megatrends Inc. Standard System Module BIOS, BN 9306-9397.01 Wandel & Goltermann Technologies, Inc 003712 KB ok Wait .......

\*\*\*\*\*\*\*

The BIOS test takes about 10 s to complete. If no faults are detected, a single long beep is output. If errors have been detected, appropriate error messages are displayed if this is possible. Otherwise, audible warning is given (see chapter 4.2).

The AT-CPU configuration detected during the BIOS tests and as set in the CMOS setup is displayed. The operating system (DOS) is then loaded from the memory board (flash ROM).

The AUTOEXEC.BAT file on drive C: is processed. The graphics software and instrument software are then loaded from the memory board (flash ROM). A memory manager (extended DOS) is loaded to allow the the operating system and instrument software to use the memory area above 640 kB.

The instrument (measurement) software is started.

If the instrument software starts correctly, a beep is output.

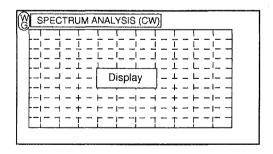

After starting the "main" software, the crossover switch on the display control board (BSK-3) is switched to the VGA ---> CRT setting. This means that the subsequent output to the EL display is generated by the graphics processor (TI processor of the BSK-3). The output to any externally connected monitor is via the VGA module of the BSK-3 from now on.

The measurement display is shown. The instrument is ready for use.

Fig. 4-1 Screen displays during normal boot-up (power-on) of the instrument

### 4.2 BIOS-Test (Power-On Test) Error Messages [Series A to E]

A power-on test (AT-CPU BIOS test) is performed when the instrument is switched on (compare chapter 4.1, "Normal SNA Boot-Up Behavior (Series A to E)"). The tests performed and the error messages which may be displayed depend on the AT-CPU (BIOS version and manufacturer) used in the SNA. The following refers to the AT-CPU "STANDARD SYSTEM MODULE 386 WGR" (3011.9305.006) used in instruments from series A through E.

The BIOS test checks practically all of the functions of the AT-CPU. The basic functions of the following modules are also tested:

- Display control board

- Keyboard controller

- Floppy disk drive

The value of the BIOS TEST is somewhat limited due to the bus system used (CONTROL BUS). In addition to the above-mentioned boards, the memory and interface boards are also connected to this bus. If one of the boards causes a bus conflict, the result of the BIOS test does not allow identification of a defective module.

If an error occurs during these tests, audible and visual warnings are output. These are useful for tracing faults in the control unit. Attention should be paid to the audible warnings (duration and sequence of beeps) which may occur during the boot-up procedure (immediately after switching on).

# The self test (BIOS TEST) has been completed successfully when a long BEEP is heard (see "Normal SNA Boot-Up Behavior (Series A to E)" on page 4-1)

After this, the instrument software is loaded automatically.

The following indicates how faults in the control unit can be traced; examples of possible error conditions and their causes are used for this.

*Note:* It is assumed that the supply voltages for the instrument are correct for the following troubleshooting procedure. It is therefore a good idea to check the supply voltages to the control unit circuit boards first (see block diagram in Service Manual Annex).

# Electroluminescent display remains blank after switch-on - audible warnings

#### Beep sequence: 1 x long beep approx. 10 seconds after switching on

The beep indicates that the BIOS has been completed successfully. The fault is therefore either in the display control board (BSK-3) or in the EL display. The function of the display control board can be checked by connecting an external monitor. If the monitor screen also remains blank, the display control board is faulty. Otherwise, the EL display DS1 must be checked for faults or the complete unit (16) exchanged.

*Important:* The external monitor only shows a display if the crossover switch on the display control board (BSK-3) switches from the VGA module to the TI graphics processor (GSP) for the EL display. This occurs when the measurement display is or would normally be shown on the built-in EL display (see "Normal SNA Boot-Up Behavior (Series A to E)" on page 4-1).

### Beep sequence: 1 x long and 3 x short; 1 x long and 8 x short

A fault was detected on the display control board during the test (e.g. the VGA BIOS for the BSK-3 could not be loaded). Clear the fault by replacing the display control board (BSK-3).

### Beep sequence: 3 x long

A fault occurred during the test of the first 64 kB of the RAM on the AT CPU. Clear the fault by replacing the AT CPU.

# Electroluminescent display lights up (normal boot-up) - audible warnings

### Beep sequence: continuous sequence of short beeps

The instrument boots-up normally until the message "Starting MS-DOS" appears. The long beep (indicating a successful BIOS test) is **not** output and the instrument software is **not** loaded.

This fault condition indicates an error during the keyboard test. Possible causes are a stuck key or a fault in the keyboard controller.

### Other possible fault conditions

The BIOS test displays an error message on the EL display. Most of the tests apply to the AT CPU itself. The remaining tests apply to the display control board, the keyboard controller and the floppy disk drive. The error messages indicate which of these modules is the likely source of the fault.

### 4.3 Error Messages / Faulty Behavior After Successful BIOS Test (Series A to E)

#### Introduction

After the BIOS test, first the operating system (DOS) and then the instrument software will be loaded and started. The operating system and the instrument software are both stored on drive C:, which is the memory board (FLASH ROM DISK). The SNA's AT-CPU configuration has this drive (C:) set as the BOOT drive (set in the extended BIOS which is also loaded from the memory board FLASH ROM DISK). If the AT CPU cannot "find" the extended BIOS, e.g. due to a defect on the memory board, the operating system can be loaded from a bootable floppy disk.

If the AT CPU loads the extended BIOS, the operating system can only be loaded from a floppy disk if this is labelled "WAGO\_BOOT". The service disk can be used in such cases.

*Note:* If errors occur during loading of the instrument software or during measurements, first check the settings in the CMOS setups for the AT CPU (see chapter 4.5 on page 4-9).

### Operating system/instrument software does not load

#### Operating system does not load

If the memory board (17) is not detected during the BIOS test (extended BIOS is not loaded), drive C: does not exist for the SNA. The instrument behaves like a normal PC and attempts to load the operating system from the floppy drive (drive A:).

Error message: DRIVE NOT READY ERROR

insert BOOT diskette in A: Press any key when ready

Possible causes: Memory board (17) defective, FLASH EPROMS U400, U401 on

memory board (17) completely or partially erased or defective.

Error in control unit (e.g. CONTROL BUS conflict)

Remedy: To locate the error, first boot the SNA from a floppy disk (e.g. service

disk). If the operating system loads from the disk, the prompt A:\ is displayed. Next, try to re-install the instrument software from the floppy disks. If this is not possible, the memory board (17) should be

repaired or replaced and the software re-installed.

If the SNA will not boot from the floppy disk, the fault is in the control

unit.

Error message: General failure reading drive B

Abort, Retry, Fail?

Note: This error message indicates that the data and compensation tables

stored on drive B: are faulty or have been erased (see chapter 4.7 on

page 4-15).

Possible causes: SRAM (drive B:) on the memory board (17) defective, lithium battery

on the memory board (17) defective.

Remedy: To locate the fault, first check the lithium battery on the memory

board. Then place the "Compensation Data" disk in drive A: and switch on the SNA. The operating system is loaded from the disk and the compensation data are copied into the RAM disk (drive B:). If this is not possible, the memory board should be replaced or repaired, after which the compensation data and the instrument software

should be reinstalled (see chapter 4.6 on page 4-14).

If the SNA will not boot from the disk either, the fault is located in the

control unit.

#### Operating system/instrument software does not load

If the memory board (17) is detected during the boot-up procedure (extended BIOS is loaded), the SNA attempts to load the operating system and then the instrument software from drive C:. If errors occur, various error messages may be output or the SNA may lock up completely. As a check that the extended BIOS has loaded, attempt to access drives C: and B: from the DOS prompt by entering the DOS commands <C:> or <B:> followed by <dir>. If the drive directory is displayed, the extended BIOS has been loaded from the memory board.

Possible causes:

Memory board defective, FLASH EPROMS on memory board (17)

partly or completely erased or defective.

Remedy:

To locate the fault, first boot the SNA from a disk (e.g. service disk). If the operating system loads from the disk, the prompt A:\ is displayed. Now try to reinstall the instrument software from disk (see chapter 4.6 on page 4-14). If this is not possible, repair or replace the memory

board and then reinstall the instrument software.

If the SNA will not boot from the disk either, the fault is located in the

control unit.

Note:

The above error scenario indicates that at least part of the memory board is working correctly as the extended BIOS could be loaded from U400 and U401 on the memory board. If this were not the case, the error message DRIVE NOT READY ERROR would appear.

### 4.4 Error messages during measurements

If a major hardware fault occurs after the instrument software has been loaded or during measurements, the measurement program is aborted and appropriate error messages are displayed on the screen ("2101 Debug Output" is displayed). The error messages allow localization of the fault in a limited sense.

### 4.4.1 2101 Debug Output

If a so-called Fatal Error occurs during operation of the SNA, the instrument software aborts and the message "2101 Debug Output" is displayed. Figure 4-2 shows an example of the 2101 Debug Output message. The error messages are shown in boldface type. The SNA is in DOS mode after exiting from the operating software.

#### BN2101 debug output

selector of main() = 0x017F

14:34:31

2194316 Bytes of memory available

main: starting

1663956 Bytes of memory available

INTERNAL ERROR <0>: Download error ZF-DSP 0x3000

CommunicationError from ZF-DSP in ZF\_Get\_PegKorrLoc. ErrorCode = 3005

Error 3005: ZF\_Get\_PegKorrLoc

Error 3005: WriteRam from daten\_tablog not ok! Error 3005: WriteRam from daten\_tablin not ok!

INTERNAL ERROR <0>: Download error Synthe 0x3000

CommunicationError from ZF-DSP in ZF\_Set\_Vbw. ErrorCode = 3005

FATAL ERROR <3005>: ZF\_DSP\_Error in ZF\_Handler

program terminated at

14:34:42

C:\

Fig. 4-2 Example "2101 Debug Output" display

A large number of Internal Errors may occur and be displayed before the instrument software is terminated by a "Fatal Error". These Internal Errors are useful in tracing the cause of a fault as they can indicate the cause of the subsequent Fatal Error and hence the cause of program termination. The events leading up to a Fatal Error are therefore of interest in troubleshooting. Evaluation of the 2101 Debug Output message must always begin with the first error message displayed.

*Note:* The display of the SNA cannot be scrolled in this mode. If a large number of errors have occurred, it is possible that the screen will only display the last error messages before the fatal error. The header line of the 2101 Debug Output page indicates whether some messages have been overwritten or not. If the header "2101 Debug Output" is still visible at the top of the display, this means that all of the error messages are displayed. If this header is no longer displayed, some of the messages have been overwritten and cannot be displayed.

The entire contents of the 2101 Debug Output message are also stored in the file B:\SNA.ERR so that all of the error messages can be read even if they do not fit onto a single display page.

#### Displaying the contents of the file B:\SNA.ERR

The instrument is in DOS mode when the instrument software is aborted by an error. The "2101 Debug Output" message is displayed, followed by the DOS prompt C:.

Important: Connect an external keyboard for making the following entries.

Now make the following entries in the order given, confirming each entry by pressing Return:

- B: Switch to drive B (RAM disk, battery buffered RAM on the

memory board).

TYPE SNA.ERRIMore This displays the complete contents of the file SNA.ERR page

by page on the display.

The character | is obtained by simultaneously pressing [Alt Gr] +

[<,>] on the external keyboard.

### Caution!

The contents of SNA.ERR will be overwritten by the error messages occurring during the new boot-up if the SNA is switched off and then on again. The original error messages will be lost if different errors occur during the new boot-up procedure.

The contents of SNA.ERR can be displayed more conveniently by using the DOS editor. Enter EDIT to load the editor. Open the file B:\SNA.ERR to display it. The file can be printed out from the editor.

You can also save the file B:\SNA.ERR to a disk in drive A: by using the "SAVE AS" command in the "FILE" menu of the DOS editor.

This file can then be read and printed out using any PC with a word processor program.

Important: See the DOS manual for details of how to use the editor function.

### 4.5 AT CPU CMOS Setup (Series A to E)

#### 4.5.1 Introduction

The correct CMOS setup is necessary for the SNAs processor (AT CPU) to operate correctly. The settings are stored in a battery-buffered RAM module in the AT CPU (the RAM module and battery are part of the AT-CPU clock module). The setup program uses menus (in English) The following settings are possible (required) for the STANDARD CMOS SETUP for the CPU used in the SNA:

- Date:

mn (month)

date

(the day of the week is entered automatically from the date)

year

Time:

hour min sec

Hard Disk C: Type:

Hard Disk D: Type:

Hard Disk C: Type: \(\) Number from a table predefining the hard disk parameters.

Hard Disk D: Type: J Enter no. 47 to select a user-defined hard disk.

If this is done, all disk parameters (Cyln, Head, WPcom etc.) must be

entered manually.

Floppy Drive A:

Floppy Drive B:

Type (capacity) dof the floppy drive installed

- Primary Display:

Type of graphics board installed.

- Keyboard:

Selects whether keyboard test is performed during boot-up or not.

The size of the DRAM on the CPU (BASE MEMORY, Ext. Memory) is determined during booting of the CPU and is entered in the appropriate menu fields. These values cannot be altered.

Settings affecting the hardware for the AT-CPU must be made using the ADVANCED CMOS SETUP program. The SNA only allows setting of the "Shadow RAM Option".

### 4.5.2 Invoking the CMOS Setup Program

The AT CPU CMOS setup program can be started in various ways. Different methods are used to access the CMOS setup menu, depending on whether an external keyboard is connected to the SNA or not.

#### Invoking the CMOS setup program using an external keyboard

With the SNA switched off, connect an external keyboard to the SNA. Press and hold down the Delete key on the external keyboard, and switch on the SNA. Hold the Delete key down until the setup menu appears (see fig. 4-3).

#### Invoking the CMOS setup program using the built-in instrument keyboard

Switch on and wait until the message "Wandel & Goltermann, Spectrum and Network Analyzer SNA XY" is displayed. Then press and hold down the DEL key of the instrument until the setup menu appears (see fig. 4-3).

*Note:* The message "Hit <DEL> If you want to run SETUP" appears briefly. DEL must be pressed before this message disappears, otherwise the instrument will not branch to the setup program and the instrument software will be loaded (see "Normal SNA Boot-Up Behavior (Series A to E)"). If the instrument software loads, switch off the SNA and try again.

### Setup menu display

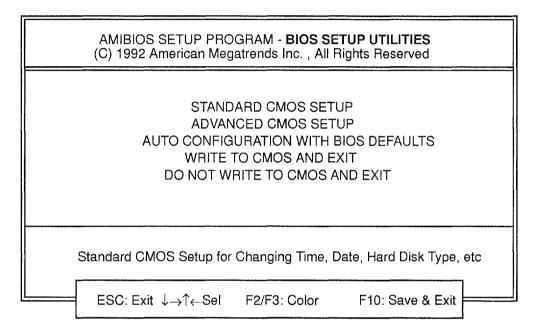

Fig. 4-3 Screen display after invoking the setup program

Figure 4-3 shows the (initial) setup menu. The bottom line of the menu containing the operating hints is not visible on the built-in EL display of the SNA. For this reason, all of the more important setup menu displays are reproduced in the figures which follow.

### 4.5.3 Using the CMOS Setup Program

### Using an external keyboard

See chapter 4.10 for connecting an external keyboard.

If the setup menu is displayed (see fig. 4-3) the cursor keys  $\downarrow \rightarrow \uparrow \leftarrow$  can be used to select the various menu items (STANDARD CMOS SETUP, ADVANCED CMOS SETUP etc.) When the RETURN key  $(\leftarrow)$  is pressed, the program branches to a warning menu which indicates the consequences of making an incorrect entry in the setup. Pressing RETURN  $(\leftarrow)$  again displays the sub-menu which was selected.

The keys have the following functions when an external keyboard is used to operate the setup program:

Cursor keys  $\downarrow \rightarrow \uparrow \leftarrow$ :

Select menu item / field

PgUp, PgDn:

Change field content / Select option

ESC:

Return to initial menu

Return ←:

Invoke / confirm selection made

### Using the built-in keyboard

The keys have the following functions when the built-in keyboard is used to operate the setup program:

J↑:

Select menu item / field

$ZOOM \leftrightarrow$ :

Change field content / Select option

ESC:

Return to initial menu

Enter:

Invoke / confirm selection made

SWEEP:

Y (YES)

HOLD:

N (NO)

### 4.5.4 SNA-20/23 CMOS Setup Settings

#### STANDARD CMOS SETUP

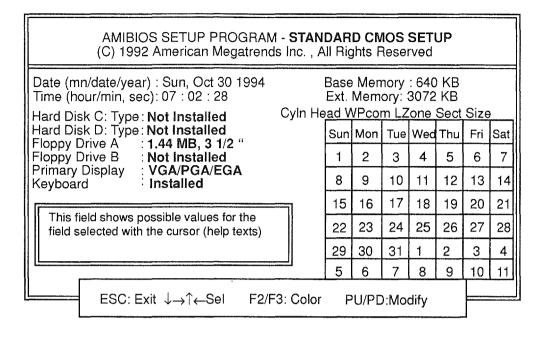

Fig. 4-4 Standard CMOS Setup values and options (Series A to E)

Figure 4-4 shows the STANDARD CMOS SETUP sub-menu. The values entered in the menu (shown in boldface type) are the values prescribed for the SNA and must be set to these values for the SNA to function correctly, with the exception of the date and time values which should be set to the appropriate current date and time.

The help text window shows possible settings, options and explanantions for the field selected by the cursor.

#### ADVANCED CMOS SETUP

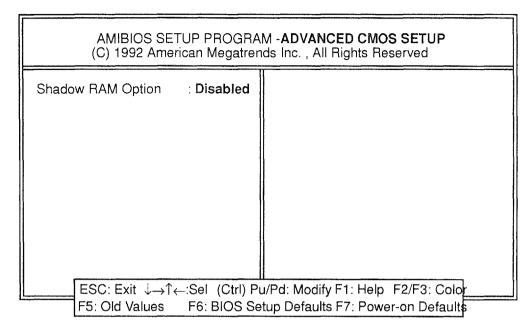

Fig. 4-5 Advanced CMOS Setup values and options (Series A to E)

The SNA ADVANCED CMOS SETUP (see fig. 4-5) only allows setting of the "Shadow RAM Option". The "Disabled" setting must be selected to ensure that the instrument operates correctly.

### 4.5.5 Ending the Setup Program

Once all the settings are correct, the program can be terminated. If setup settings were changed (corrected), terminate the program using the "Write to CMOS and Exit" command.

#### Exit without saving

If no settings were altered, exit the program using the "DO NOT WRITE TO CMOS AND EXIT" command. Press the ESC key to return to the initial menu and then select this menu item (see below under "Using a country-specific external keyboard").

### Exit and save

If settings were altered, you must exit the program using the "WRITE TO CMOS AND EXIT" command to write the changes to the CMOS RAM of the CPU for them to become effective (see below under "Using a country-specific external keyboard").

#### Using a country-specific external keyboard

When exiting from the setup program, the program requests a N (No) or Y (Yes) response before the program can be ended. The setup program uses the US-standard keyboard driver. If you are using a non-US keyboard, some of the key functions may be different (e.g. on a German keyboard, the positions of the "Z" and "Y" keys are reversed). Press the key on your keyboard which corresponds to the "N" or "Y" key on the US keyboard to respond to the exit query. This does not affect the use of the built-in keyboard (see "Using the built-in keyboard" on page 4-11).

Please also refer to chapter 4.10.

### 4.6 Installing the Instrument Software / Updating Software

The instrument software will need to be installed if the memory board is replaced or repaired. Insert disk no.1 in the floppy drive (A:) of the SNA and switch the instrument on. The software is installed automatically. From time to time during the installation, you will be asked to confirm various messages by pressing a key. The screen also indicates when the next floppy disk is to be inserted (the disk number will be displayed). The instrument software is stored on drive C: (Flash ROM disk).

Use the same procedure for installing software updates.

The compensation data for the instrument (see chapter 4.7) and any user-specific settings or setups are not affected by loading the instrument software, as they are stored on drive B:\ (battery-buffered SRAM on the memory board (17)) of the SNA. If these files are lost or damaged, they must also be reinstalled (see chapter 4.7).

### 4.7 Installing the Compensation Data

The extreme accuracy of the SNA-20/-23 can only be achieved by calibration of various circuit modules and subassemblies. This compensation data is stored in the form of tables in the instrument and is used to correct measurements during operation of the SNA. A floppy disk containing a backup copy of the the compensation data specific to the instrument is included with each SNA.

The following compensation data is determined and stored for each individual SNA:

Frequency response correction, Band 0

Frequency response correction, Band 1

Frequency response correction, Band 2

Frequency response correction, Band 2

Frequency response correction, Band 3

File: SNA\DATA\ fckor\_b1.tab (SNA-23)

File: SNA\DATA\ fckor\_b2.tab (SNA-23)

File: SNA\DATA\ fckor\_b3.tab (SNA-23)

File: SNA\DATA\ pkor\_lin.tab

File: SNA\DATA\ pkor\_log.tab

### Instruments with memory board (17) [Series A to E]

The specific compensation data are stored on RAM disk (battery buffered SRAM on the memory board (17)). The RAM disk is drive B:\. The compensation data will need to be reinstalled if this board is repaired or replaced, or if the Lithium battery on the board fails. Insert the "Compensation Data" disk in floppy drive A:\ of the SNA and switch on the instrument. The installation of the files is then automatic. During installation, a message appears to indicate that all user-specific settings have been lost. Once you confirm this message by pressing any key, drive B:\ is formatted and the required data are copied from drive A:. Once this has been completed, remove the floppy disk from drive A: and press any key to reboot the SNA automatically.

#### Caution!

Loading the compensation data deletes all user setups. If such information is stored in the instrument, make a back-up copy of it before installing the compensation data (see chapter 4.8 on page 4-15).

### 4.8 Saving User Setups on Floppy Disk

Before making repairs to the instrument, user-specific intrument settings (setups) should be backed up to floppy disk. This is particularly important if the memory board (17) is to be repaired or replaced or if the Lithium battery on this board is replaced.

Insert a formatted disk in drive A:\ of the SNA. In the MODE/DOS UTILITIES menu, press the BACKUP RAM SETUPS TO FLOPPY softkey to save the user setups to the floppy disk.

Once repairs have been completed, the setups can be restored to the RAM from the same menu. Switch on the instrument and insert the floppy disk containing the saved setups into drive A:\. Press the RESTORE RAM SETUPS FROM FLOPPY to read the setups from the disk and write them back to the battery-buffered RAM in the SNA.

### 4.9 Making a Back-Up Copy of RAM Disk B:\

(Applies only to instruments fitted with memory board (17) [Series A to E])